# End of Life Derating: A Necessity or Overkill

Application Note November 1999 AN9867

Author: J. E. Vinson, Ph.D., Sr. Principal Engineer, Reliability, jvinson@intersil.com

### Abstract

Customers have the practice of derating the performance specifications for integrated circuits. This may come from a carryover of derating discrete components or from a lack of knowledge about the parts. The practice is expensive in the terms of part performance. It also may provide large system margin and make the assembly more expensive than is required. This paper describes the way data sheet limits are specified at Intersil Corporation and why derating of these limits is not necessary. These parts are intended for use in space worthy systems.

### **Index Terms**

Derating Parts, End of Life Predictions, Reliability, and Data Sheet Limits

### Introduction

#### What is it?

Derating a part involves relaxing some characteristic about the part. As an example, a 200V capacitor may be limited to 100V when operated at 125°C. The capacitor has been derated 50% because of temperature. Another example is with resistors. A 1W resistor may be used in a high temperature application but only allow 1/4W of power dissipation. This is a 75% deration of power because of the operational temperature. Many different characteristics can be derated. In addition to the above of voltage or power, one could derate current handling ability or switching speed. Any measured or specified value can be derated.

#### Why is it Used?

Derating indicates an envelope of operation for a device. Using the resistor example above we reduced the allowed power being produced in the resistor. This power produces a temperature rise in the resistor. For temperature above "the safe operational" temperature the reliability of the resistor is jeopardized. For a numerical example consider a resistor that is rate at 1W with an ambient temperature of 75°C. The resistor has a 50°C temperature rise with this power, so the internal temperature is 125°C. To maintain the same maximum temperature of the resistor for higher ambient, the power must be reduced. If the part operates at 100°C, then the allowed power would be reduced to about 1/2W. This is where derating comes into play.

### When is it Appropriate?

Derating should always be used if the parameter is specified on the data sheet with derating curves or similar nomenclature. The natural response would be to derate all parameters to insure adequate margin in the system design. The difficulty produced by this mind set is the lack of

understanding how the data sheet limits were determined. It could be that the data sheet limits have a 6-sigma margin built into them. If a customer were to derate everything by 50% then the system would have many times the 2x margin expected. This approach adds cost and reduces performance. In today's competitive market a more useful approach would be to understand the limits and how they were determined and what they mean to the part's performance and reliability.

This paper is designed to provide insights into how data sheet limits are determined and what impact these parameters have for customers of Intersil's Radiation Hardened Integrated Circuits. The paper outlines the product development and qualification approach used at Intersil and also reviews the on-going reliability evaluation used for these hardened integrated circuits.

# **Product Development**

### Concept Phase

The development of a part begins at concept review with a preliminary set of datasheet limits used as design goals for the part. These limits are defined by the customer's needs and the ability of the process technology and circuit function to meet the requirements. These requirements include operational speed, delay times, operating supply current, reliability and other measurable parameters. The fabrication process is selected and the concept of how to implement the circuit functions in that process is reviewed.

### Design Phase

The design phase is the phase where the schematic is developed detailing how the circuit elements are sized and connected to implement the required function. At this point design tradeoffs may require compromises. A typical example is the need to consume more supply current (power) to increase the speed of operation. Optimization along critical delay paths includes proper sizing of the transistor elements to prevent race conditions. After the design is completed the circuit must be implemented in silicon. This is the layout phase of the design. Here a skilled technician places the circuit element in a logical order using a computer aided design system. The design system has rules checkers that allow design rules to be reviewed electronically. This includes spacing as well as reliability rules. Spacing rules are required to meet the limitation of the wafer process, to define metal lines, diffusions, and similar features. The reliability rules include electromigration and other factors that affect the reliability of the part.

Once the part is completely laid out a parasitic extraction is performed. This operation allows the parasitic resistance,

capacitance and in some cases inductance to be included in the simulation. A new simulation is performed including the parasitic elements to insure the design goals are still being met. If they are not then adjustments to the layout or design is required. This process is repeated until the desired results are obtained. Once this occurs the data base is ready to be built in silicon.

### **Product Introduction**

#### **Product Characterization**

The first wafer fabrication lots built are used for product characterization and qualification. The first of these tasks is discussed here and the qualification effort is discussed in the next section. Characterization is used to set the datasheet limits on parts. This includes reviewing all parameters included in the datasheet over temperature and radiation for the parts that are radiation hardened. A sample of 100 units from at least 2 wafer runs is used in the characterization.

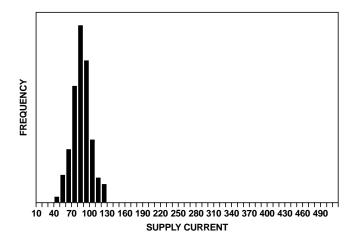

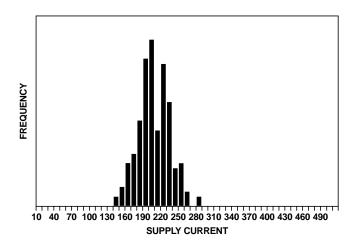

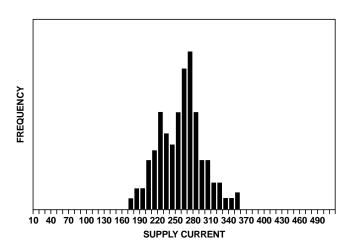

The product is tested using a production worthy test program design to measure the parameters desired in the datasheet. The data from this testing is collected and statistically analyzed. A 6-sigma datasheet limit is typically used to set the datasheet limit. This means that the datasheet limit is 6 standard deviations away from the mean of the measured population for that parameter. Populations are selected for each temperature and the post radiation environment. An example of typical distributions for supply current is shown in Figures 1 to 3. These figures show 3 supply current distributions for a hypothetical part over three different environments: Room Temperature (25°C), High Temperature (125°C), and High Temperature (125°C) Post Radiation (300KRads-Si). In the datasheet a parameter may have a limit that is over temperature and another one that is for radiation. In many cases, the datasheet limit is for both temperature and radiation. In some cases, Intersil also uses an internal screening limit for room temperature to remove the outlyers shown in Figure 2. These higher than normal parts can cause reliability failures later in life test. The user should read and understand the datasheet and follow its direction carefully. In cases where the user is not sure they should contact an Applications Engineer for further assistance.

### **Product Qualification**

The product qualification is performed in parallel with the characterization. The qualification includes doing multiple tests to insure the reliability of the parts. Two examples of tests performed on hermetic parts are high temperature operating life (HTOL) testing and temperature cycling (TC). HTOL applies bias to the part at an elevated temperature to accelerate aging of the defective population. The defective population or infant mortality portion fails quickly where the intrinsic population remains alive. The reader is directed to my other paper (AN9654, Use of Life Tested Parts, http://www.intersil.com/data/an/an9/an9654/) for a discussion of the use of life tested parts.

FIGURE 1. ROOM TEMPERATURE SUPPLY CURRENT DISTRIBUTION

FIGURE 2. HIGH TEMPERATURE SUPPLY CURRENT DISTRIBUTION

FIGURE 3. HIGH TEMPERATURE, POST RADIATION SUPPLY CURRENT DISTRIBUTION

The electrical parameters measured during the life testing are the same ones measured during product characterization. As a part of the data review the drift of these parameters is monitored. A failure is defined as anything that does not meet the datasheet limits for that parameter. A sub set of these measured parameters is reviewed for drift to determine if any movement in the parameters occurs during life testing. If significant movement is observed failure analysis determines its cause and correction action is implemented prior to the product's release.

The current release criteria for a new product include less than 1% failure during the screening burn-in of 168 hours. If more than 1% of the parts fail then failure analysis must determine root cause. This is followed by a corrective action plan. Additional burn-in may be required to verify that the corrective action was successful in correcting the problem. The 1% criterion is much tighter than normal production burn-in. Production burn-in allows up to 5% failure without action. The reason for this is to detect systematic failures that would cause issues during production.

The passing parts from the burn-in are sampled using a sampling plan of LTPD = 3% or LoT Percent Defective equal to 3%. This sampling plan states in words that if the sample passes there will be less than 3% defective in the lot 95% of the time. A sample size of 129 parts is sampled and one failure is allowed. Failure analysis is required on all qualification failures. No systematic failures are allowed. A systematic failure is one caused by the design, layout, or process that are not random defects. This LTPD is also a tighter requirement than is imposed during normal production. In normal production the typical sample plan is to an LTPD = 5%. The qualification phase looks at a new product under tighter requirements so there will be less likelihood of issues during production. All qualification failures are analyzed to determine the cause. The duration of the life test can range from 1000 hours to 3000 hours at 125°C or equivalent. The variation depends on the maturity of the process. For new parts on a new process with only a few parts qualified the life test will last until 3000 hours. After many parts are successfully qualified on the process the time will decrease to 1000 hours.

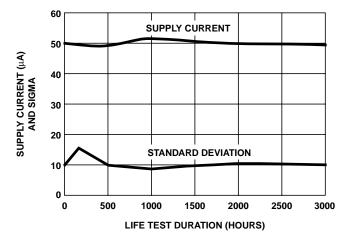

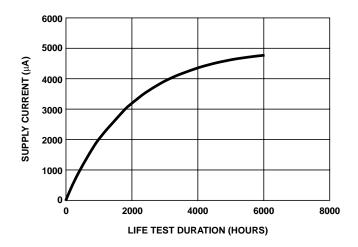

As a part of the qualification effort a data analysis is done to look for drift in specific parameters. Key parameters for the drift analysis are supply current, input leakage, timing specifications. The drift analysis is used to look for instabilities in the population that may cause failures at a later time. Figure 4 shows a data analysis graph of our hypothetical part for supply current. For illustration purposes, Figure 5 shows a data analysis for a part with sodium contamination. The amount of shift will saturate because the amount of active contaminate is limited. Sodium, potassium, lithium and other Group I metals on the Periodic Table of elements can contaminate a semiconductor circuit. This

contamination introduces positive ions into the oxides. Under bias the ions move and can cause transistors to turn-on where they should not be. This results in an increase in supply current. The rate at which they drift is dependent on the electric field and the temperature. Most current fabrication methods have all but eliminated this failure mechanism. Multiple tests during wafer fabrication look for this type of failure.

FIGURE 4. SUPPLY CURRENT DRIFT AS A FUNCTION OF LIFE TEST DURATION - TYPICAL PART

FIGURE 5. SUPPLY CURRENT DRIFT AS A FUNCTION OF LIFE TEST DURATION - SODIUM CONTAMINATED PART

All drifts in circuit performance are caused by one or more failure mechanisms. Examples of these mechanisms are electromigration, ionic contamination, hot carrier injection, and dielectric rupture. Each of these ages a device. Once the device has aged enough it fails. In many of these mechanisms the parametric shift in device operation is negligible and no shift in operation is apparent until the device fails. Examples of this type of failures are dielectric rupture and electromigration. For dielectric rupture, and

## **Application Note 9867**

oxide continues to remain an insulator until it ruptures. When it ruptures a short is formed loading an internal node of the circuit. This results in a sudden increase in supply current or a complete loss of functionality. Electromigration is similar except for a metal line. Electromigration voids the metal line up to the point where the line became an open circuit. Once an open circuit occurs an internal node is separated from the remaining circuits. This causes a loss of functionality as well as increased supply current from the floating conditions on the internal nodes. Failure mechanisms in current product typically do not cause parametric shift. When the device fails, there is a large shift in the measured parameters and subsequent failure in device operation.

### **Product Sign-off**

Once the characterization and qualification efforts are completed the product is ready to be signed off for order entry and shipments. The sign off process includes all the parties involved with manufacturing and supporting the parts after it is introduced to the market place. The data is reviewed and accepted. A signed off product meets or exceeds the data sheet limits and is shown to be reliable to those limits.

# Ongoing Evaluations

#### **Burn-in Evaluations**

Space product is evaluated on a wafer fabrication lot basis for infant mortality. This is includes a high temperature burnin performed on 100% of the packaged product. The parts reliability level governs the duration of the burn-in. The space application flow (Class T) is shorter in duration the high reliability Class V flow. The parts are tested using limits based on the datasheet. In many cases these limits are guardbanded. This means that a parameter is tested to a limit that is tighter than the specification requires to remove tester variability. In some cases a type of guardband is also applied to the temperature extremes. The part will be tested a few degrees hotter or colder to take into account variations in the temperature forcing equipment. This insures the parts supplied to the customer meets the datasheet limits and are not marginal.

Catastrophic failures (opens and shorts at room temperature) are always analyzed. In addition to this if a lot of product has greater than 5% but less than 20% failures it is recycled through burn-in for an additional burn-in cycle and the lot is retested to a tighten percent defective allowable, typically 3%. The failures are also analyzed to determine if a systematic failure mode is present. Lots with greater than 20% failures are put on hold pending failure analysis to determine what course of action is warranted.

### **QCI - Quality Conformance Inspection**

Routine reliability testing is built into the flow for space level product. This is covered in the Quality Conformance Testing. The frequency of testing is governed by the "Class" of product being manufactured. The highest class, Class V, is tested on a per test-lot basis. Each test-lot has a battery of test is must pass to be allowed to ship. One of these tests is HTOL (high temperature operational life). Here the life test sample is again tested against the datasheet limits. In general, the sample size is chosen to allow none or 1 failure. Any failures are sent for failure analysis to determine the cause of failure as well as to determine any corrective action needed in the manufacture of this part from wafer fabrication through assembly.

### **Conclusions**

Derating of Intersil's parts is not necessary. The preliminary data sheet limits are first used to design the parts electrical performance. Once actual devices are obtained characterization set the datasheet limits to be 6-sigma from the mean of the measured parameters. During the manufacturing process the parts are measured to these datasheet limits and are evaluated for shifts to these limits. The parts are consistent with these limits and are reliable as shown by the HTOL testing.

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com

# Sales Office Headquarters

NORTH AMERICA

Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902

TEL: (321) 724-7000 FAX: (321) 724-7240 EUROPE

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111

FAX: (32) 2.724.2111

**ASIA**

Intersil (Taiwan) Ltd. 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China TEL: (886) 2 2716 9310

FAX: (886) 2 2715 3029